# Wireless HDL Toolbox™ Reference

# MATLAB&SIMULINK®

R

**R**2021**b**

# **How to Contact MathWorks**

Latest news:

Phone:

www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

$\searrow$

508-647-7000

# The MathWorks, Inc. 1 Apple Hill Drive Natick, MA 01760-2098

Wireless HDL Toolbox<sup>™</sup> Reference

© COPYRIGHT 2017 - 2021 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### Trademarks

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

$MathWorks\ {\tt products}\ {\tt are}\ {\tt protected}\ {\tt by}\ {\tt one}\ {\tt or}\ {\tt more}\ {\tt U.S.}\ {\tt patents}.\ {\tt Please}\ {\tt see}\ {\tt www.mathworks.com/patents}\ {\tt for}\ {\tt more}\ {\tt information}.$

#### **Revision History**

| September 2017<br>March 2018<br>September 2018<br>March 2019<br>September 2019<br>March 2020<br>September 2020<br>March 2021<br>September 2021 | Online only<br>Online only<br>Online only<br>Online only<br>Online only<br>Online only<br>Online only<br>Online only | New for Version 1.0 (Release 2017b)<br>Revised for Version 1.1 (Release 2018a)<br>Revised for Version 1.2 (Release 2018b)<br>Revised for Version 1.3 (Release 2019a)<br>Revised for Version 1.4 (Release 2019b)<br>Revised for Version 2.0 (Release 2020a)<br>Revised for Version 2.1 (Release 2020b)<br>Revised for Version 2.2 (Release 2021a)<br>Revised for Version 2.3 (Release 2021b) |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| September 2021                                                                                                                                 | Online only                                                                                                          | Revised for Version 2.3 (Release 2021b)                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                             |

|   | Blocks    |

|---|-----------|

| 1 |           |

|   |           |

|   |           |

|   | Functions |

| 2 |           |

| ' |           |

# **Blocks**

# **Frame To Samples**

Convert frame-based data to sample stream Library: Wireless HDL Toolbox / I/O Interfaces

# Description

The Frame To Samples block flattens frame-based input into a stream of samples. The block also returns a stream of corresponding control signals that indicate sample validity and the boundaries of the frame. You can configure idle cycles inserted between samples or between frames, and how many values represent each sample. See "Streaming Sample Interface" for details of the streaming format.

Use this block to generate input for a subsystem targeted for HDL code generation. This block does not support HDL code generation.

# Ports

Input

# frame — Frame of input samples

column vector

Frame of input samples, specified as a column vector. All samples in the vector are considered valid. Each frame must be the same size.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | Boolean | fixed point

# Output

# sample — Output sample stream

scalar | vector

Output sample stream, returned **Output size** values at a time. The output stream includes idle samples as specified by **Idle cycles between samples** and **Idle cycles between frames**. Each output sample has a corresponding set of control signals on the **ctrl** port.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | Boolean | fixed point

# ctrl — Control signals accompanying sample stream

samplecontrol bus

Control signals accompanying the sample stream, returned as a samplecontrol bus. The bus includes the start, end, and valid control signals, which indicate the boundaries of the frame and the validity of the samples.

- **start** Indicates the start of the output frame

- end Indicates the end of the output frame

- valid Indicates that the data on the output data port is valid

For more detail, see "Sample Control Bus".

Data Types: bus

# **Parameters**

# **Idle cycles between samples — Number of idle cycles to insert after each sample** 0 (default) | integer

Number of idle cycles to insert after each sample, specified as a scalar integer. The block returns a vector of **Output size** zeros for each idle cycle and sets all control signals to 0 (false).

Idle cycles between frames — Number of idle cycles to insert at the end of each frame 0 (default) | integer

Number of idle cycles to insert at the end of each frame, specified as a scalar integer. The block returns a vector of **Output size** zeros for each idle cycle and sets all control signals to 0 (false).

# **Output size — Number of values representing each sample**

1 (default) | positive integer

Number of values representing each sample, specified as a positive integer scalar. The block outputs a vector of **Output size** values. Each vector has one corresponding set of control signals. For example, you can use this parameter to serialize turbo-encoded samples. In the LTE standard, the turbo code rate is 1/3, so each sample is represented by one systematic value and two parity values:  $S_n$ ,  $P1_n$ , and  $P2_n$ . In this case, set **Output size** to 3.

# Compose output from interleaved input samples — Order of output samples relative to input order

off (default) | on

Order of output samples relative to input order, when more than one value represents each sample. For example, for 1/3 turbo-encoded samples, the input frame can be ordered [S\_1 P1\_1 P2\_1 S\_2 P1\_2 P2\_2] or [S\_1 S\_2 P1\_1 P1\_2 P2\_1 P2\_2]. In the first case, the output is two vectors, [S\_1 P1\_1 P2\_1] and [S\_2 P1\_2 P2\_2]. To achieve the same output in the second case, select **Compose output from interleaved input samples**.

# Dependencies

This parameter applies when **Output size** is greater than one.

# **Extended Capabilities**

# C/C++ Code Generation

Generate C and C++ code using Simulink<sup>®</sup> Coder<sup>m</sup>.

This block supports C/C++ code generation for Simulink<sup>®</sup> accelerator and rapid accelerator modes and for DPI component generation.

# See Also

**Blocks** Samples To Frame

**Functions** whdlFramesToSamples

Introduced in R2017b

# **Samples To Frame**

Convert sample stream to frame-based data Library: Wireless HDL Toolbox / I/O Interfaces

# Description

The Samples To Frame block reconstructs frame-based data from a stream of samples and its corresponding control signals. It removes any idle or nonvalid samples from the data. See "Streaming Sample Interface" for details of the streaming format.

Use this block to process output from a subsystem targeted for HDL code generation. This block does not support HDL code generation.

# Ports

# Input

# sample — Stream of samples

scalar | vector

Stream of samples, specified as a scalar or vector. Vector input values represent a single sample, such as turbo-encoded samples represented by one systematic value and two parity values. The stream can include idle cycles between samples and between frames. Idle samples are discarded. double and single are supported for simulation but not for HDL code generation.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | Boolean | fixed point

# ctrl — Control signals accompanying sample stream

samplecontrol bus

Control signals accompanying the sample stream, specified as a samplecontrol bus. The bus includes the start, end, and valid control signals, which indicate the boundaries of the frame and the validity of the samples.

- start Indicates the start of the input frame

- end Indicates the end of the input frame

- valid Indicates that the data on the input data port is valid

For more detail, see "Sample Control Bus".

Data Types: bus

# Output

#### frame — Frame of output samples

column vector

Frame of output samples, returned as a column vector. Each frame is the same size. If the input frame is smaller than **Output size**, the block pads the frame with zeroes. If the output frame is larger than the **Output size**, the block forms the frame by using the first **Output size** samples. You can optionally output the number of valid samples in each frame on the **len** port.

# valid — Validity of output frame

scalar

Validity of output frame, returned as a Boolean scalar. This port returns 1 (true) when the values on the **frame** and **len** (optional) ports, are valid.

Data Types: Boolean

# len — Number of valid samples in output frame

integer

Number of valid samples in output frame, returned as an integer. The input sample stream can have frames of different sizes. The block returns a constant size vector on the **frame** port, padded with zeroes when the input frame is smaller than **Output size**. The **len** port indicates how many valid samples are in the output frame. If the output frame is larger than the **Output size**, the block forms the frame by using the first **Output size** samples.

Data Types: double

# Parameters

# Input size — Number of values representing each sample

1 (default) | positive integer

Number of values representing each sample, specified as a positive integer scalar. The block accepts a vector of **Input size** values. Each vector has one corresponding set of control signals. For example, you can use this parameter for turbo-encoded samples. In the LTE standard, the turbo code rate is 1/3, so each sample is represented by one systematic value and two parity values:  $S_n$ ,  $P1_n$ , and  $P2_n$ . In this case, set **Input size** to 3.

# Frame search window — Number of input cycles to buffer

1 (default) | positive integer

Number of input cycles to buffer before attempting to form an output frame, specified as an integer. The block simulates faster when this parameter is larger. However, the block returns at most one frame from each search window. If more than one frame fits in this window, the block returns the first one it finds and drops the later frames. The default setting, 1 cycle, never drops frames, but results in slower simulation. Therefore, it is a best practice to set this parameter to the minimum number of cycles per frame, including idle cycles.

For example, calculate the valid cycles and idle cycles representing each frame. Each cycle may include more than one sample, depending on your **Input size** (*samplesize*) setting.

```

% Exact setting: includes idle cycles

totalframesize = ((framesamples/samplesize)*...

(idlecyclesbetweensamples+1))+idlecyclesbetweenframes;

```

If the frame and sample spacing is variable or unknown, then a conservative compromise is to set the **Frame search window** to the minimum number of valid cycles per frame. For instance, for a turbo encoder block, the output frame size depends on the coding rate, 1/R, and tail bits specified by the LTE standard. The output data has R samples per cycle. This calculation does not include any idle cycles between samples or between frames.

```

% Conservative setting: number of valid output cycles, without idles

encoderrate = 3;

numtailbits = 12;

framesize = (framesamples+numtailbits)/encoderrate;

```

# Output size — Maximum samples per frame

1024 (default) | positive integer

Maximum number of samples per frame, specified as an integer. The input sample stream can have frames of different sizes. The block returns a constant size vector, padded with zeroes if the frame is smaller than **Output size**. If the block receives a frame larger than **Output size**, it truncates the frame.

# Compose output from interleaved input samples — Order of output samples relative to input order

off (default) | on

Order of output samples relative to input order, when more than one value represents each sample. For example, 1/3 turbo-encoded samples are represented by  $[S_1 P1_1 P2_1]$  and  $[S_2 P1_2 P2_2]$ . The default output order is  $[S_1 P1_1 P2_1 S_2 P1_2 P2_2]$ . To reorder the samples so that systematic and parity values are grouped together, select **Compose output from interleaved input samples**. The output order is then  $[S_1 S_2 P1_1 P1_2 P2_1 P2_2]$ .

# Enable frame length output port — Output number of valid samples

off (default) | on

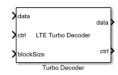

Enable frame length output port. Select this option to return the number of valid samples in each output frame. The length is returned on the **len** port and is qualified by the **valid** signal. Use this option when the sample stream has variable size frames or when a downstream block requires the frame size as input, such as LTE Turbo Decoder.

# **Extended Capabilities**

# C/C++ Code Generation

Generate C and C++ code using Simulink® Coder<sup>™</sup>.

This block supports C/C++ code generation for Simulink accelerator and rapid accelerator modes and for DPI component generation.

# See Also

**Blocks** Frame To Samples

# Functions

whdlSamplesToFrames

# Introduced in R2017b

# **FIL Frame To Samples**

Convert frame-based data to sample stream for FPGA-in-the-loop Library: Wireless HDL Toolbox / I/O Interfaces

# Description

The FIL Frame To Samples block performs the same frame-to-sample conversion as the Frame To Samples block. It returns output data as vectors of the entire frame of samples. The block returns control signal vectors of the same width as the sample data. This optimization makes more efficient use of the communication link between the FPGA board and your Simulink simulation when using FPGA-in-the-loop (FIL). To run FPGA-in-the-loop, you must have an HDL Verifier<sup>™</sup> license.

When you generate a programming file for a FIL target in Simulink, the tool creates a model to compare the FIL simulation with your Simulink design. For Wireless HDL Toolbox<sup>™</sup> designs, the FIL block in that model replicates the sample-streaming interface to send one sample at a time to the FPGA. You can modify the autogenerated model to use the FIL Frame To Samples and FIL Samples To Frame blocks to improve communication bandwidth with the FPGA board by sending one frame at a time. For how to modify the autogenerated model, see "FPGA-in-the-Loop".

# Ports

Input

# frame — Frame of input samples

column vector

Frame of input samples, specified as a column vector. All samples in the vector are considered valid. Each frame must be the same size.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | Boolean | fixed point

# Output

# sampleN — Sample stream

vector

Stream of samples, returned as a vector representing an entire frame. The output stream includes idle cycles between samples and between frames as specified in the block parameters.

If you set **Output size** greater than one, the block shows one port for each output value. In this case, a single sample is represented by N values, such as turbo-encoded samples represented by one systematic value and two parity values. The output data is one vector for each port.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | Boolean | fixed point

# start — Start of frame

vector

Start of frame, returned as a **Boolean** vector containing one value for each sample in the frame. This signal is 1 (true) for one timestep corresponding to the first valid sample of the frame.

Data Types: Boolean

#### end — End of frame

vector

End of frame, returned as a **Boolean** vector containing one value for each sample in the frame. This signal is 1 (true) for one timestep corresponding to the last valid sample of the frame.

Data Types: Boolean

#### valid — Validity of samples

vector

Validity of samples, returned as a **Boolean** vector containing one value for each sample in the frame. This signal is 1 (true) on timesteps that correspond to valid samples.

Data Types: Boolean

# **Parameters**

# **Idle cycles between samples — Number of idle cycles to insert after each sample** 0 (default) | integer

Number of idle cycles to insert after each sample, specified as a scalar integer. The block returns a zero on each **sampleN** port for each idle cycle and sets all control signals to 0 (false).

# Idle cycles between frames — Number of idle cycles to insert at the end of each frame 0 (default) | integer

Number of idle cycles to insert at the end of each frame, specified as a scalar integer. The block returns a zero on each **sampleN** port for each idle cycle and sets all control signals to 0 (false).

#### **Output size — Number of values representing each sample**

1 (default) | positive integer

Number of values representing each sample, specified as a positive integer scalar. The block has **Output size** output sample ports. The control signals apply to all **sampleN** ports.

For example, you can use this parameter to serialize turbo-encoded samples. In the LTE standard, the turbo code rate is 1/3, so each sample is represented by one systematic value and two parity values:  $S_n$ ,  $P1_n$ , and  $P2_n$ . In this case, set **Output size** to 3.

Compose output from interleaved input samples — Order of output samples relative to input order

off (default) | on

Order of output samples relative to input order, when more than one value represents each sample.

For example, for 1/3 turbo-encoded samples, the input frame can be ordered [S\_1 P1\_1 P2\_1 S\_2 P1\_2 P2\_2] or [S\_1 S\_2 P1\_1 P1\_2 P2\_1 P2\_2]. In the first case, the output is two vectors, [S\_1 P1\_1 P2\_1] and [S\_2 P1\_2 P2\_2]. To achieve the same output in the second case, select **Compose output from interleaved input samples**.

#### Dependencies

This parameter applies when **Output size** is greater than one.

# **Extended Capabilities**

#### C/C++ Code Generation

Generate C and C++ code using Simulink® Coder<sup>™</sup>.

This block supports C/C++ code generation for Simulink accelerator and rapid accelerator modes and for DPI component generation.

# See Also

Frame To Samples | FIL Samples To Frame

**Topics** "Streaming Sample Interface" "FPGA-in-the-Loop"

Introduced in R2017b

# **FIL Samples To Frame**

Convert sample stream from FPGA-in-the-loop to frame-based data Library: Wireless HDL Toolbox / I/O Interfaces

# Description

The FIL Samples To Frame block performs the same sample-to-frame conversion as the Samples To Frame block. It accepts input data as vectors of the entire frame of samples. The block expects control signal input vectors of the same width as the sample data. This optimization speeds up the communication link between the FPGA board and your Simulink simulation when using FPGA-in-the-loop. To run FPGA-in-the-loop, you must have an HDL Verifier license.

When you generate a programming file for a FIL target in Simulink, the tool creates a model to compare the FIL simulation with your Simulink design. For Wireless HDL Toolbox designs, the FIL block in that model replicates the sample-streaming interface to send one sample at a time to the FPGA. You can modify the autogenerated model to use the FIL Frame To Samples and FIL Samples To Frame blocks to improve communication bandwidth with the FPGA board by sending one frame at a time. For how to modify the autogenerated model, see "FPGA-in-the-Loop".

# Ports

# Input

# sampleN — Stream of samples

vector

Stream of samples, specified as a vector representing an entire frame. The stream can include idle cycles between samples and between frames. Idle samples are discarded.

If you set **Number of input samples** greater than one, the block shows one port for each input value. In this case, a single sample is represented by N values, such as turbo-encoded samples represented by one systematic value and two parity values. The input data is one vector for each port. The control signals apply to all **sampleN** ports.

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | Boolean | fixed point

# start — Start of frame

vector

Start of frame, specified as a **Boolean** vector containing one value for each sample in the frame. This signal is 1 (true) for one timestep corresponding to the first valid sample of the frame.

Data Types: Boolean

#### end — End of frame

vector

End of frame, specified as a **Boolean** vector containing one value for each sample in the frame. This signal is 1 (true) for one timestep corresponding to the last valid sample of the frame.

Data Types: Boolean

#### validIn — Validity of samples

vector

Validity of samples, specified as a **Boolean** vector containing one value for each sample in the frame. This signal is 1 (true) on timesteps that correspond to valid samples.

Data Types: Boolean

#### Output

#### frame — Frame of output samples

column vector

Frame of output samples, returned as a column vector. Each frame is the same size. If the input frame is smaller than **Output size**, the block pads the frame with zeroes. If the output frame is larger than the **Output size**, the block forms the frame by using the first **Output size** samples. You can optionally output the number of valid samples in each frame on the **len** port.

#### validOut — Validity of output frame

scalar

Validity of output frame, returned as a Boolean scalar. This port returns 1 (true) when the values on the **frame** and **len** (optional) ports, are valid.

Data Types: Boolean

# len — Number of valid samples in output frame

integer

Number of valid samples in output frame, returned as an integer. The input sample stream can have frames of different sizes. The block returns a constant size vector on the **frame** port, padded with zeroes when the input frame is smaller than **Output size**. The **len** port indicates how many valid samples are in the output frame. If the output frame is larger than the **Output size**, the block forms the frame by using the first **Output size** samples.

Data Types: double

# **Parameters**

# Number of input samples — Number of values representing each sample

1 (default) | positive integer

Number of values representing each sample, specified as a positive integer scalar. The block has one **sampleN** port for each value. The control signals apply to all **sampleN** ports. For example, you can use this parameter for turbo-encoded samples. In the LTE standard, the turbo code rate is 1/3, so each sample is represented by one systematic value and two parity values: *S\_n*, *P1\_n*, and *P2\_n*. In this case, set **Number of input samples** to 3.

# Output size — Maximum samples per frame

1024 (default) | positive integer

Maximum number of samples per frame, specified as an integer. The input sample stream can have frames of different sizes. The block returns a constant size vector, padded with zeroes if the frame is smaller than **Output size**. If the block receives a frame larger than **Output size**, it truncates the frame.

# Compose output from interleaved input samples — Order of output samples relative to input order

off (default) | on

Order of output samples relative to input order, when more than one value represents each sample. For example, 1/3 turbo-encoded samples are represented by  $[S_1 P1_1 P2_1]$  and  $[S_2 P1_2 P2_2]$ . The default output order is  $[S_1 P1_1 P2_1 S_2 P1_2 P2_2]$ . To reorder the samples so that systematic and parity values are grouped together, select **Compose output from interleaved input samples**. The output order is then  $[S_1 S_2 P1_1 P1_2 P2_1 P2_2]$ .

# **Enable frame length output port — Output number of valid samples** off (default) | on

Enable frame length output port. Select this option to return the number of valid samples in each output frame. The length is returned on the **len** port and is qualified by the **valid** signal. Use this option when the sample stream has variable size frames or when a downstream block requires the frame size as input, such as LTE Turbo Decoder.

# **Extended Capabilities**

# C/C++ Code Generation

Generate C and C++ code using Simulink  $\mbox{\ensuremath{\mathbb{R}}}$  Coder<sup>TM</sup>.

This block supports C/C++ code generation for Simulink accelerator and rapid accelerator modes and for DPI component generation.

# See Also

FIL Frame To Samples | Samples To Frame

#### **Topics** "Streaming Sample Interface" "FPGA-in-the-Loop"

# Introduced in R2017b

# **Sample Control Bus Creator**

Create control signal bus for use with Wireless HDL Toolbox blocks Library: Wireless HDL Toolbox / Utilities

# Description

The Sample Control Bus Creator block creates a samplecontrol bus for modeling streaming control signals in communication systems for hardware. See "Sample Control Bus".

The block is an implementation of the Simulink Bus Creator block. See Bus Creator for more information.

# Ports

Input

# start — Start of frame

scalar

Start of frame, specified as a **Boolean** scalar. This signal is 1 (true) for one time step, corresponding to the first valid sample of the frame.

Data Types: Boolean

#### end — End of frame

scalar

End of frame, specified as a **Boolean** scalar. This signal is 1 (true) for one time step, corresponding to the last valid sample of the frame.

Data Types: Boolean

# valid — Validity of samples

scalar

Validity of samples, specified as a **Boolean** scalar. This signal is 1 (true) on time steps that correspond to valid samples.

Data Types: Boolean

# Output

# ctrl — Control signals accompanying sample stream

samplecontrol bus

Control signals accompanying the sample stream, returned as a samplecontrol bus. The bus includes the start, end, and valid control signals, which indicate the boundaries of the frame and the validity of the samples.

- start Indicates the start of the output frame

- end Indicates the end of the output frame

- \* valid Indicates that the data on the output data port is valid

For more detail, see "Sample Control Bus".

Data Types: bus

# **Extended Capabilities**

# C/C++ Code Generation

Generate C and C++ code using Simulink  $\mathbb{R}$  Coder<sup> $\mathbb{M}$ </sup>.

This block supports C/C++ code generation for Simulink accelerator and rapid accelerator modes and for DPI component generation.

# HDL Code Generation

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

HDL Coder  $^{\text{\tiny TM}}$  provides additional configuration options that affect HDL implementation and synthesized logic.

To learn more about using buses for HDL code generation, see "Buses" (HDL Coder) and "Use Bus Signals to Improve Readability of Model and Generate HDL Code" (HDL Coder).

#### **HDL Architecture**

This block has a single, default HDL architecture.

#### **HDL Block Properties**

| ConstrainedOutputPi<br>peline | Number of registers to place at the outputs by moving existing delays<br>within your design. Distributed pipelining does not redistribute these<br>registers. The default is 0. For more details, see<br>"ConstrainedOutputPipeline" (HDL Coder). |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| InputPipeline                 | Number of input pipeline stages to insert in the generated code.<br>Distributed pipelining and constrained output pipelining can move these<br>registers. The default is 0. For more details, see "InputPipeline" (HDL<br>Coder).                 |

| OutputPipeline                | Number of output pipeline stages to insert in the generated code.<br>Distributed pipelining and constrained output pipelining can move these<br>registers. The default is 0. For more details, see "OutputPipeline" (HDL<br>Coder).               |

# See Also

# Blocks

Frame To Samples | Samples To Frame | Sample Control Bus Selector | Bus Creator

# Functions

whdlFramesToSamples | whdlSamplesToFrames

**Topics** "Streaming Sample Interface" "Sample Control Bus"

# Introduced in R2017b

# **Sample Control Bus Selector**

Select signals from the control signal bus used with Wireless HDL Toolbox blocks Library: Wireless HDL Toolbox / Utilities

# Description

The Sample Control Bus Selector block selects signals from the samplecontrol bus. This bus is used for modeling streaming control signals in communication systems for hardware. See "Sample Control Bus".

The block is an implementation of the Simulink Bus Selector block. See Bus Selector for more information.

# Ports

# Input

# ctrl — Control signals accompanying sample stream

samplecontrol bus

Control signals accompanying the sample stream, specified as a samplecontrol bus. The bus includes the start, end, and valid control signals, which indicate the boundaries of the frame and the validity of the samples.

- **start** Indicates the start of the input frame

- end Indicates the end of the input frame

- valid Indicates that the data on the input data port is valid

For more detail, see "Sample Control Bus".

Data Types: bus

# Output

# start — Start of frame

scalar

Start of frame, returned as a **Boolean** scalar. This signal is 1 (true) for one time step, corresponding to the first valid sample of the frame.

Data Types: Boolean

end — End of frame scalar

End of frame, returned as a **Boolean** scalar. This signal is 1 (true) for one time step, corresponding to the last valid sample of the frame.

Data Types: Boolean

# valid — Validity of samples

scalar

Validity of samples, returned as a **Boolean** scalar. This signal is 1 (true) on time steps that correspond to valid samples.

Data Types: Boolean

# **Extended Capabilities**

# C/C++ Code Generation

Generate C and C++ code using Simulink® Coder<sup>™</sup>.

This block supports C/C++ code generation for Simulink accelerator and rapid accelerator modes and for DPI component generation.

# HDL Code Generation

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

HDL Coder provides additional configuration options that affect HDL implementation and synthesized logic.

To learn more about using buses for HDL code generation, see "Buses" (HDL Coder) and "Use Bus Signals to Improve Readability of Model and Generate HDL Code" (HDL Coder).

#### **HDL Architecture**

This block has a single, default HDL architecture.

#### HDL Block Properties

| ConstrainedOutputPi<br>peline | Number of registers to place at the outputs by moving existing delays<br>within your design. Distributed pipelining does not redistribute these<br>registers. The default is 0. For more details, see<br>"ConstrainedOutputPipeline" (HDL Coder). |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| InputPipeline                 | Number of input pipeline stages to insert in the generated code.<br>Distributed pipelining and constrained output pipelining can move these<br>registers. The default is 0. For more details, see "InputPipeline" (HDL<br>Coder).                 |

| OutputPipeline                | Number of output pipeline stages to insert in the generated code. Distributed pipelining and constrained output pipelining can move these registers. The default is $0$ . For more details, see "OutputPipeline" (HDL Coder).                     |

# See Also

# Blocks

Frame To Samples | Samples To Frame | Sample Control Bus Creator | Bus Selector

# Functions

whdlFramesToSamples | whdlSamplesToFrames

# Topics

"Streaming Sample Interface" "Sample Control Bus"

# Introduced in R2017b

# Depuncturer

Reverse puncturing scheme to prepare for decoding Library: Wireless HDL Toolbox / Error Detection and Correction

| data         |             | data    |

|--------------|-------------|---------|

| > puncVector | Depuncturer | valid   |

| valid        |             | erasure |

# Description

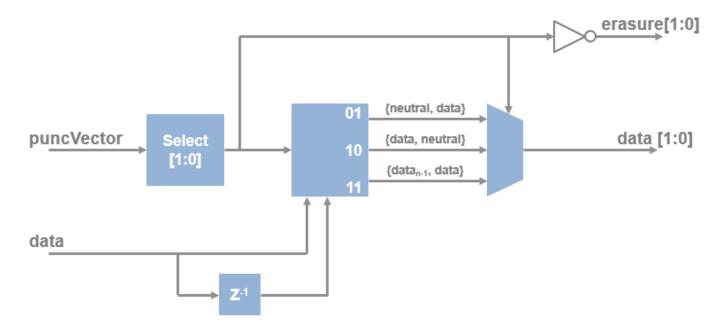

The Depuncturer block replaces punctured symbols with neutral values as directed by an input puncture vector. The block returns erasure bits, which indicate the presence of neutral symbols in the output data stream. The block supports continuous and frame modes of operation. It provides an interface and architecture suitable for HDL code generation and hardware deployment.

Many wireless communication standards implement different code rates by puncturing patterns with a base code rate 1/2. The input to the block is a stream of one sample at a time. You can provide samples represented by hard-decision binary values or soft-decision log-likelihood ratios (LLR). The block returns output samples as 2-by-1 vectors.

The inserted neutral value depends on the data type of the input sample. For details, see the input **data** port.

# Ports

Input

# data — Input sample

scalar

| the data type of the input samples. |                        |

|-------------------------------------|------------------------|

| Input Data Type                     | Inserted Neutral Value |

| • boolean                           | 0                      |

| • fixdt(0,1,0)                      |                        |

| fixdt(0,WL,0)                       | 2 <sup>(WL-1)</sup>    |

| uint8                               | 128                    |

| uint16                              | 32768                  |

| • fixdt(1,WL,0)                     | 0                      |

| • int8                              |                        |

| • int16                             |                        |

| • single                            |                        |

| • double                            |                        |

Input sample, specified as a scalar. The block inserts a neutral value at punctured locations based on the data type of the input samples.

The block treats the input as hard-decision samples when the input type is Boolean or fixdt(0,1,0). For signed and unsigned numeric types, the block assumes soft-decision samples. The block treats samples as signed integers for single and double data types, but these data types are not supported for HDL code generation.

The input sample must have a word length less than or equal to 16 bits, and a fraction length of 0 bits.

Data Types: int8 | int16 | uint8 | uint16 | Boolean | fixdt(0,1,0) | fixdt(S,WL,0) | single | double

# puncVector — Puncture vector

column vector of binary values

Puncture vector, specified as a column vector of binary values. The length of the puncture vector must be an even number in the range [4, 28]. The length must remain constant. The block removes initial zeros from the provided vector, up to the first 1 (true). After the first 1 (true), the puncture vector cannot contain any [1:0] subvector matching [0 0].

For example, IEEE 802.11 WLAN standard [1] supports puncture rates 2/3, 3/4, and 5/6, with respective vector lengths of 4, 6, and 10. To support these multiple rates, set **Puncture vector source** to Input port. To support the largest vector size, the vector length must be 10 for all rates. For 2/3 and 3/4 rates, pad the **puncVector** input with zeros to create a 10-element vector. The puncture vector for rate 3/4 is [1 1 0 1 1 0]'. For a vector length of 10, use [0 0 0 0 1 1 0 1 1 0]' as the input **puncVector**.

When **Operation mode** is set to **Continuous**, the block captures the value of **puncVector** when both the **syncPunc** and input **valid** ports are 1 (true).

When **Operation mode** is set to Frame, the block captures the value of **puncVector** when both **ctrl.start** and **ctrl.valid** are 1 (true).

#### Dependencies

To enable this port, set **Puncture vector source** to Input port.

Data Types: Boolean

# syncPunc — Puncture synchronization signal

scalar

Puncture synchronization signal, specified as a Boolean scalar value. This input is a control signal that synchronizes the puncture vector input with the input sample. When both **syncPunc** and **valid** are 1 (true), the block aligns the puncture vector to begin puncturing. The block captures the vector from either the **puncVector** input port or the **Puncture vector** parameter. The block ignores the **puncVector** port when **syncPunc** is 0 (false).

# Dependencies

To enable this port, set **Operation mode** to **Continuous**. When **Operation mode** is **Frame**, the block synchronizes the puncture vector using control signals in the input **ctrl** bus.

Data Types: Boolean

valid — Validity of input samples

scalar

Control signal that indicates when the sample from **data** input port is valid. When **valid** is 1 (true), the block captures the values of the **data** input port. When **valid** is 0 (false), the block ignores the input samples.

#### Dependencies

#### To enable this port, set **Operation mode** to **Continuous**.

Data Types: Boolean

#### ctrl — Control signals accompanying sample stream

samplecontrol bus

Control signals accompanying the sample stream, specified as a samplecontrol bus. The bus includes the start, end, and valid control signals, which indicate the boundaries of the frame and the validity of the samples.

#### Dependencies

To enable this port, set **Operation mode** to Frame.

Data Types: bus

#### Output

# data — Output sample

2-by-1 column vector

Output sample, returned as a 2-by-1 column vector. The data type is same as the data type of the input samples.

Data Types: int8 | int16 | uint8 | uint16 | Boolean | fixdt(0,1,0) | fixdt(S,WL,0) | single | double

#### valid — Validity of output data samples

scalar

Control signal that indicates when the sample from the **data** output port is valid. The block sets the **valid** port to 1 (true) when there is a valid sample on the output **data** port.

#### Dependencies

Tho enable this port, set **Operation mode** to Continuous.

Data Types: Boolean

#### ctrl — Control signals accompanying sample stream

samplecontrol bus

Control signals accompanying the sample stream, returned as a samplecontrol bus. The bus includes the start, end, and valid control signals, which indicate the boundaries of the frame and the validity of the samples.

#### Dependencies

#### To enable this port, set **Operation mode** to Frame.

Data Types: bus

# erasure - Neutral symbol locations

2-by-1 column vector

Neutral symbol locations, returned as a 2-by-1 column vector corresponding to the output samples. When **erasure** is 1 (true), the corresponding output **data** element is a depunctured neutral value.

Data Types: Boolean

# **Parameters**

# Operation mode — End of frame behavior

Continuous (default) | Frame

End of frame behavior, specified as one of these modes:

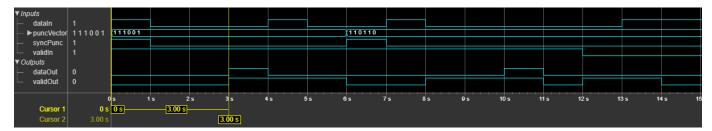

• Continuous - Allow changes to **puncVector** at any time. To force the block to capture the new puncture vector, set **syncPunc** to 1(true). This waveform shows ufix4 input samples depunctured in Continuous mode.

| ► dataIn     | 1      | 1   | 4    | 14 | 13 | 0 | 10 | 12 | 3  | 1    | 4    | 1    | X7   | 6    |    | 14  | 6  | 4  | 0  | 3          |     | 0    | 11 | 0   | 9   | 6  |

|--------------|--------|-----|------|----|----|---|----|----|----|------|------|------|------|------|----|-----|----|----|----|------------|-----|------|----|-----|-----|----|

| ► puncVector | 110110 | 11  | 0110 |    |    |   |    |    |    |      | 0 0  | 111( | )    |      |    |     |    |    |    |            |     |      |    |     |     |    |

| syncPunc     | o      |     |      |    |    |   |    |    |    |      |      |      | 1    |      |    |     |    |    |    |            |     |      |    |     |     |    |

| validIn      |        |     |      |    |    |   |    |    |    |      |      |      |      |      |    |     |    |    |    |            |     |      |    |     |     |    |

| ► dataOut    | 00     | 0 0 |      |    |    |   |    |    | 14 | 8 14 | 13 8 | 300  | 0 10 | 8 12 | 38 | 0 0 | 14 | 00 | 17 | <u>5</u> 8 | 0 0 | 6 14 | 68 | 0 0 | 4 0 | 38 |

| validOut     | o      |     |      |    |    |   |    |    |    |      |      |      |      |      |    |     |    |    |    |            |     |      |    |     |     |    |

| ► erasure    | 00     |     |      |    |    |   |    |    |    |      | )    |      |      |      | χ  |     |    |    |    |            | )   |      |    |     |     | XX |

|              |        |     |      |    |    |   |    |    |    |      |      |      |      |      |    |     |    |    |    |            |     |      |    |     |     |    |

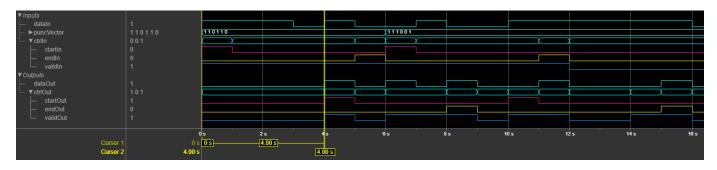

• Frame - You can only change **puncVector** at the start of a frame, indicated by **ctrl.start**. This waveform shows ufix4 input samples depunctured in Frame mode.

| I. | 1    | 9   | 3 | 6 | 9 | 4 |    | 9  | 4  | 13  | 15 | 11 | 5                  | <b>)</b> 9 | 1   | 14     |      | 13  | 4 | 9  | 0    | 6   | 5     | 2  |  |

|----|------|-----|---|---|---|---|----|----|----|-----|----|----|--------------------|------------|-----|--------|------|-----|---|----|------|-----|-------|----|--|

|    | 1101 | 110 |   |   |   |   |    |    |    |     |    |    | 0 0 1 <sup>.</sup> | 10         |     |        |      |     |   |    |      |     |       |    |  |

|    |      |     |   |   |   |   |    |    |    |     |    |    |                    | χ          |     |        |      |     |   |    |      |     |       |    |  |

|    |      |     |   |   |   |   |    |    |    |     |    |    |                    |            |     |        |      |     |   |    |      |     |       |    |  |

|    |      |     |   |   |   |   |    |    |    |     |    |    |                    |            |     |        |      |     |   |    |      |     |       |    |  |

|    |      |     |   |   |   |   |    |    |    |     |    |    |                    |            |     |        |      |     |   |    |      |     |       |    |  |

|    | 0 0  |     |   |   |   |   | 19 | 83 | 68 | 0 0 | 94 | 84 | 98                 | 0 0        | 4 1 | 3 8 15 | 11 8 | 0 0 |   | 91 | 14 8 | 0 0 | 14 13 | 48 |  |

|    |      |     |   |   |   |   |    | (  |    |     |    |    |                    |            |     |        |      |     |   | χ  |      |     |       |    |  |

|    |      |     |   |   |   |   |    |    |    |     |    |    |                    |            |     |        |      |     |   |    |      |     |       |    |  |

|    |      |     |   |   |   |   |    |    |    |     |    |    |                    |            |     |        |      |     |   |    |      |     |       |    |  |

|    |      |     |   |   |   |   |    |    |    |     |    |    |                    |            |     |        |      |     |   |    |      |     |       |    |  |

|    |      |     |   |   |   |   |    | X  | X  |     |    |    |                    |            |     |        |      |     |   |    |      |     |       |    |  |

|    |      |     |   |   |   |   |    |    |    |     |    |    |                    |            |     |        |      |     |   |    |      |     |       |    |  |

# Puncture vector source - Source of puncture vector

Input port (default) | Property

Source of puncture vector, specified as either:

- Input port Specify the puncture vector using the puncVector port.

- Property Specify the puncture vector using the Puncture vector parameter.

#### Puncture vector — Locations to insert neutral values

[1;1;0;1;1;0] (default) | column vector of binary values

Puncture vector, specified as a column vector of binary values. The length of the puncture vector must be an even number in the range [4, 28]. The default value is the puncture vector for 3/4 code rate of IEEE 802.11 WLAN [1].

The puncture vector cannot contain any [1:0] subvector matching [0 0].

#### Dependencies

To enable this port, set **Puncture vector source** to Property.

# Algorithms

The depuncturing algorithm shifts through each [1:0] subvector of the puncture vector. The subvector has three valid patterns: [0 1], [1 0], or [1 1]. Based on the subvector, neutral samples are inserted in place of punctured samples. The erasure output is the inverse of the puncture subvector. The block returns an error when it encounters the invalid subvector [0 0].

#### Latency

When you set **Operation mode** to **Continuous**, the latency from valid input to valid output in is seven cycles. When you set **Operation mode** to Frame, the latency is six cycles.

# Performance

These resource and performance data are the synthesis results from the generated HDL targeted to a Xilinx<sup>®</sup>Zynq<sup>®</sup>-7000 ZC706 board. The block is using ufix4 input samples, in continuous mode with default settings. The design achieves a clock frequency of 590 MHz.

| Resource               | Number Used |

|------------------------|-------------|

| LUT                    | 54          |

| FFS                    | 67          |

| Xilinx LogiCORE® DSP48 | 0           |

| Block RAM (16k)        | 0           |

If you set **Puncture vector source** to **Property**, the design uses fewer LUT and FFS resources.

# References

[1] IEEE Std 802.11ac<sup>™</sup>-2013 IEEE Standard for Information technology — Telecommunications and information exchange between systems — Local and metropolitan area networks — Specific requirements — Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications — Amendment 4: Enhancements for Very High Throughput for Operation in Bands below 6 GHz.

# **Extended Capabilities**

# C/C++ Code Generation

Generate C and C++ code using Simulink  $\mathbb{R}$  Coder<sup> $\mathbb{M}$ </sup>.

This block supports C/C++ code generation for Simulink accelerator and rapid accelerator modes and for DPI component generation.

# HDL Code Generation

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

HDL Coder provides additional configuration options that affect HDL implementation and synthesized logic.

#### **HDL Architecture**

This block has a single, default HDL architecture.

#### **HDL Block Properties**

| ConstrainedOutputPi<br>peline | Number of registers to place at the outputs by moving existing delays within your design. Distributed pipelining does not redistribute these registers. The default is $0$ . For more details, see "ConstrainedOutputPipeline" (HDL Coder). |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| InputPipeline                 | Number of input pipeline stages to insert in the generated code. Distributed pipelining and constrained output pipelining can move these registers. The default is $0$ . For more details, see "InputPipeline" (HDL Coder).                 |

| OutputPipeline | Number of output pipeline stages to insert in the generated code.                |

|----------------|----------------------------------------------------------------------------------|

|                | Distributed pipelining and constrained output pipelining can move these          |

|                | registers. The default is 0. For more details, see "OutputPipeline" (HDL Coder). |

# See Also

**Blocks** Viterbi Decoder | Puncturer

Introduced in R2018b

# **LTE Gold Sequence Generator**

Generate Gold sequence

Wireless HDL Toolbox / Utilities

Library:

# Description

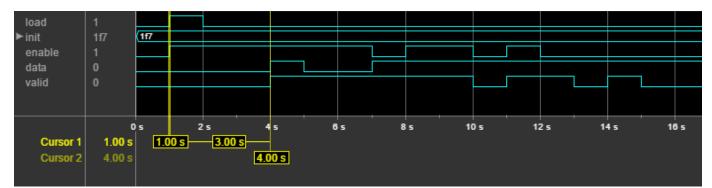

The LTE Gold Sequence Generator block returns Gold sequences generated using the polynomial and shift length specified by LTE standard TS 36.212 [1]. Gold codes are pseudorandom sequences that have high autocorrelation and low crosscorrelation. Due to these properties, Gold codes are widely used in communications systems. For example, they are used to separate different mobile cells operating on the same frequency. LTE systems use a Gold sequence generator for reference symbols and for scrambling/descrambling data, such as in MIB and SIB coding and decoding.

This block provides minimal latency by implementing the shift register initialization in parallel.

Use the **load** control signal to indicate when the **init** value is valid. Use the **enable** control signal to request the next Gold sequence value. The **valid** signal indicates when an output sample is available. The first output sample is ready three cycles after **enable** is asserted. The **data** and **valid** outputs follow the pattern of the **enable** input.

# Ports

# Input

# load — Load initial shift register value

scalar

When this control signal is set to true (1), the block loads the value on the **init** port into the shift register. You can use this signal to restart the sequence at any point in time.

Data Types: Boolean

init — Initial shift register value

scalar | vector

Initial shift register value, specified as a ufix31 number representing the 31 binary values. To generate multiple Gold sequence outputs in parallel, specify a vector of initial values to represent multiple channels.

Data Types: ufix31

enable — Enable sequence generation scalar

When this control signal is set to true (1), it enables Gold sequence generation.

Data Types: Boolean

#### Output

#### data — Generated Gold sequence

scalar | vector

Generated Gold sequence, returned as a Boolean scalar or vector, depending on the size of the **init** input. If **init** is a vector, then **data** is a vector of the same size, representing sequences on independent channels.

Data Types: Boolean

# valid — Indicates valid output data

scalar

Control signal that indicates when the **data** output port is valid.

Data Types: Boolean

# Algorithms

To avoid long shift latency, the block applies the initial value as a parallel mask. To calculate the mask, the block divides the initial polynomial by the linear-feedback shift register polynomial.

# Performance

These resource and performance data are the synthesis results from the generated HDL targeted to a Xilinx Zynq-7000 ZC706 board. The design achieves a clock frequency of 625 MHz.

| Resource        | Uses |

|-----------------|------|

| LUT             | 86   |

| LUTRAM          | 0    |

| FFS             | 107  |

| Block RAM (16K) | 0    |

# References

[1] 3GPP TS 36.212. "Multiplexing and channel coding." 3rd Generation Partnership Project; Technical Specification Group Radio Access Network; Evolved Universal Terrestrial Radio Access (E-UTRA). URL: https://www.3gpp.org.

# **Extended Capabilities**

# C/C++ Code Generation

Generate C and C++ code using Simulink® Coder<sup>™</sup>.

This block supports C/C++ code generation for Simulink accelerator and rapid accelerator modes and for DPI component generation.

# HDL Code Generation

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

HDL Coder provides additional configuration options that affect HDL implementation and synthesized logic.

# **HDL Architecture**

This block has a single, default HDL architecture.

# **HDL Block Properties**

| ConstrainedOutputPi<br>peline | Number of registers to place at the outputs by moving existing delays within your design. Distributed pipelining does not redistribute these registers. The default is $0$ . For more details, see "ConstrainedOutputPipeline" (HDL Coder). |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| InputPipeline                 | Number of input pipeline stages to insert in the generated code.<br>Distributed pipelining and constrained output pipelining can move these<br>registers. The default is 0. For more details, see "InputPipeline" (HDL<br>Coder).           |

| OutputPipeline                | Number of output pipeline stages to insert in the generated code. Distributed pipelining and constrained output pipelining can move these registers. The default is $0$ . For more details, see "OutputPipeline" (HDL Coder).               |

# See Also

# **Topics** "LTE HDL MIB Recovery"

# Introduced in R2018a

# **LTE Convolutional Decoder**

Decode convolutional-encoded samples using Viterbi algorithm Library: Wireless HDL Toolbox / Error Detection and Correction

# Description

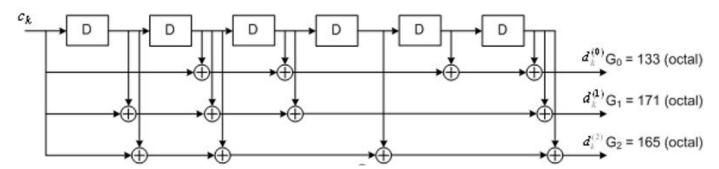

The LTE Convolutional Decoder block implements a wrap-around Viterbi algorithm (WAVA) to decode samples encoded with the tail-biting polynomials specified by LTE standard TS 36.212 [1]. The convolutional code has constraint length 7 and is tail biting with coding rate 1/3 and octal polynomials G0=133, G1=171 and G2=165. The block provides a hardware-optimized architecture and interface.

This block uses a streaming sample interface with a bus for related control signals. This interface enables the block to operate independently of frame size, and to connect easily with other Wireless HDL Toolbox blocks. The block accepts and returns a value representing a single sample, and a bus containing three control signals. These signals indicate the validity of each sample and the boundaries of the frame. To convert a matrix into a sample stream and these control signals, use the Frame To Samples block or the whdlFramesToSamples function. For a full description of the interface, see "Streaming Sample Interface".

The block accepts input samples representing soft or hard decisions. Each sample is a 3-by-1 vector, where the three values represent the bits encoded by the three polynomials,  $[G0\ G1\ G2]$ .

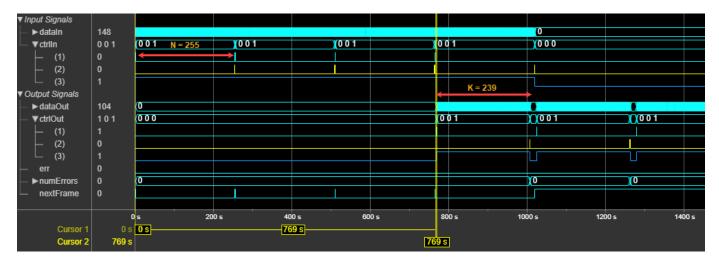

Decoding of a message of M samples requires 2\*M+140 cycles, assuming contiguous valid input. Therefore, you must leave at least that many idle cycles between input frames. Alternatively, you can use the output signal **ctrl.end** to determine when the block is ready for new input.

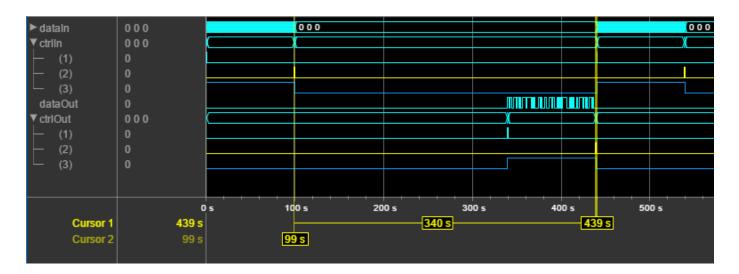

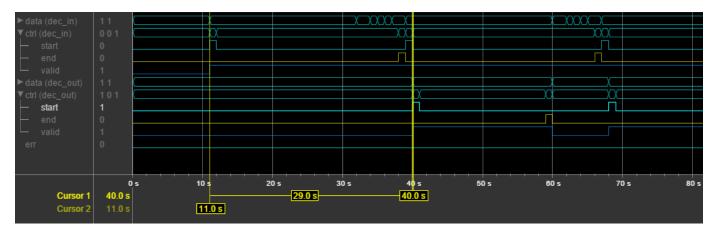

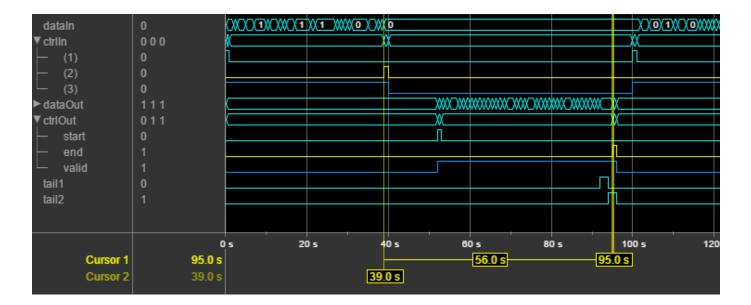

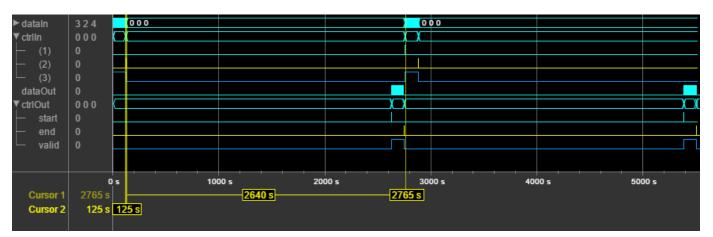

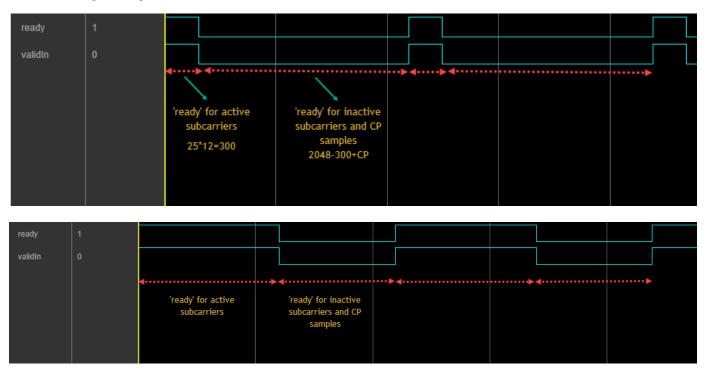

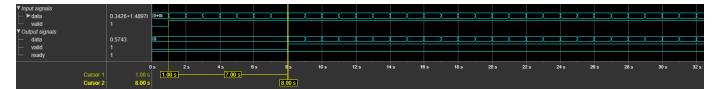

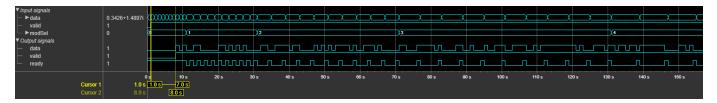

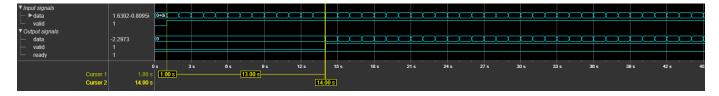

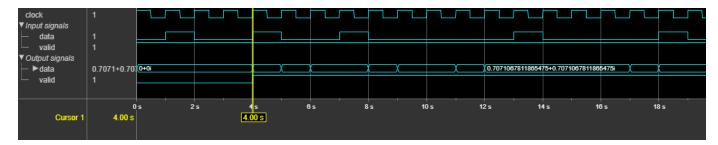

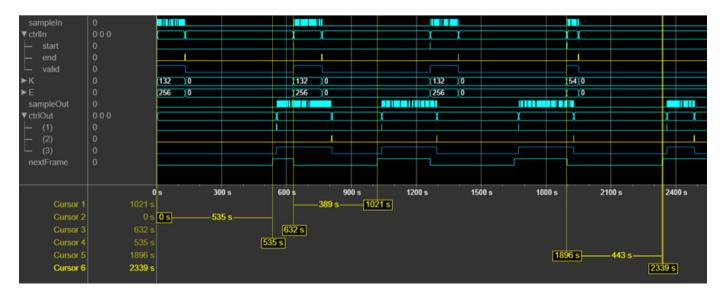

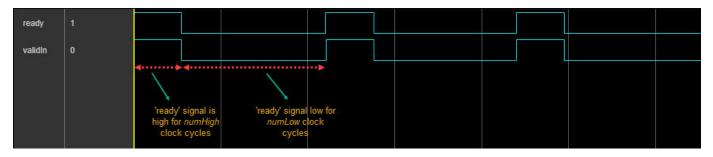

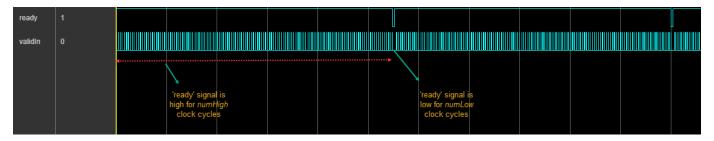

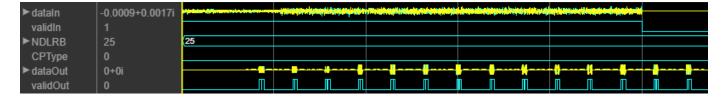

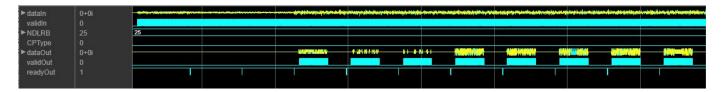

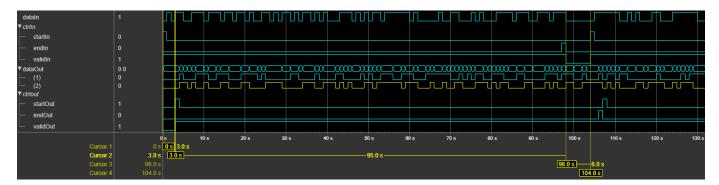

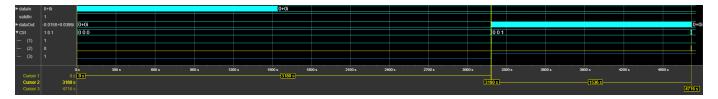

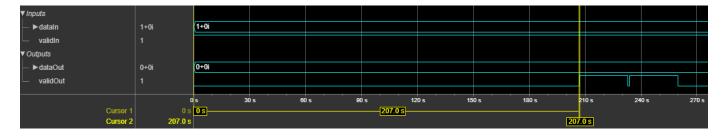

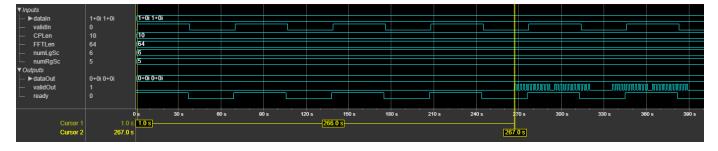

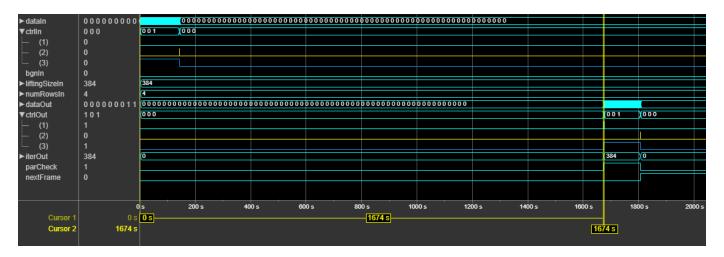

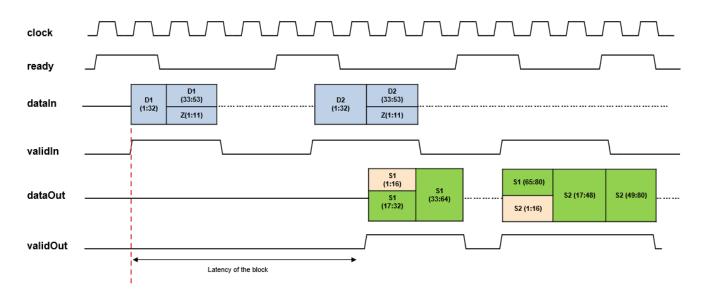

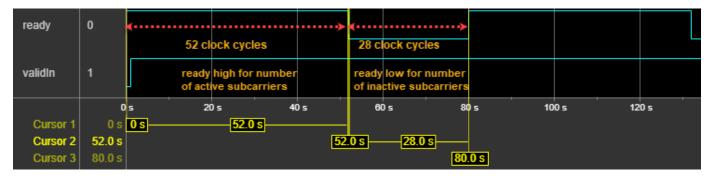

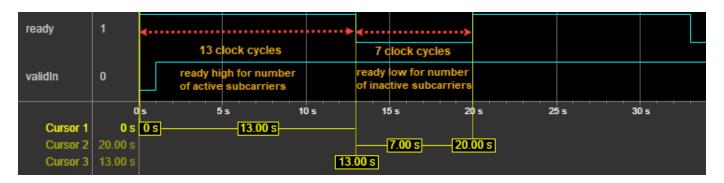

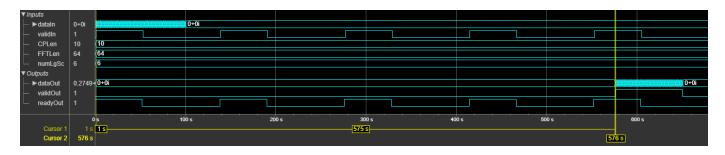

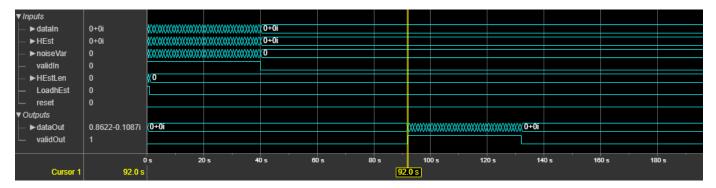

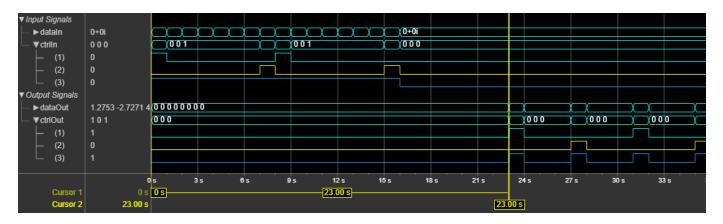

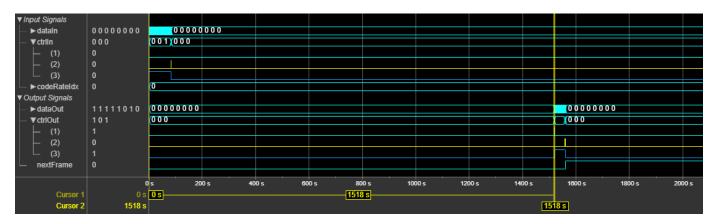

This waveform shows an input message of 100 samples, with 340 idle cycles between frames. The input data is a vector of three encoded bits. The input and output **ctrl** buses are expanded to show the control signals. **start** and **end** show the frame boundaries, and **valid** qualifies the data samples.

# Ports

## Input

## data — Input sample

3-by-1 column vector

Input sample, specified as a 3-by-1 column vector. The block performs soft-decision decoding when the input type is signed fixed point or signed integer, or performs hard-decision decoding when the input type is Boolean or fixdt(0,1,0). The block performs unquantized soft-decision decoding for single and double types, but this mode is not supported for HDL code generation.

For a hardware soft-decision implementation, an integer or fixed-point type that is three or four bits wide is recommended. This input word length achieves decode performance while optimizing timing and resource use when the design is synthesized to an FPGA. The input data type must be less than 16 bits wide. Internal data types are derived from this data type and lower precision types can result in loss of decoding performance.

Values less than zero are most likely a logical 0, while values greater than zero are most likely a logical 1. The absolute value determines the level of confidence. For example, the table shows the confidence levels used if the input is sfix4 (WL=4, FL=0).

| Soft Value  | -8, -7, -6, -5, -4, -3, -2,<br>-1 | 0       | 1, 2, 3, 4, 5, 6, 7    |

|-------------|-----------------------------------|---------|------------------------|

| Logic Level | logical 0                         | unknown | logical 1              |

| Confidence  | high $\rightarrow$ low            | none    | $low \rightarrow high$ |

Data Types: Boolean | fixdt(0,1,0) | fixdt(1,WL,FL) | int8 | int16 | single | double

## ctrl — Control signals accompanying sample stream

samplecontrol bus

Control signals accompanying the sample stream, specified as a samplecontrol bus. The bus includes the start, end, and valid control signals, which indicate the boundaries of the frame and the validity of the samples.

- **start** Indicates the start of the input frame

- end Indicates the end of the input frame

- valid Indicates that the data on the input data port is valid

For more detail, see "Sample Control Bus".

Data Types: bus

#### Output

data — Output sample

scalar

Output sample, returned as a binary scalar value.

double and single are supported for simulation but not for HDL code generation.

```

Data Types: single | double | Boolean | ufix1

```

#### ctrl — Control signals accompanying sample stream

samplecontrol bus

Control signals accompanying the sample stream, returned as a samplecontrol bus. The bus includes the start, end, and valid control signals, which indicate the boundaries of the frame and the validity of the samples.

- start Indicates the start of the output frame

- end Indicates the end of the output frame

- valid Indicates that the data on the output data port is valid

For more detail, see "Sample Control Bus".

Data Types: bus

# **Parameters**

#### Maximum message length — Maximum input frame size

1024 (default) | positive integer

Maximum input frame size, specified as a positive integer from 6 to 2048. The block uses this parameter to determine the amount of RAM required to store intermediate decisions. If you do not specify a power of two, the block uses the next largest power of two.

If an input frame is larger than the specified maximum message length, the block returns a warning.

# Algorithms

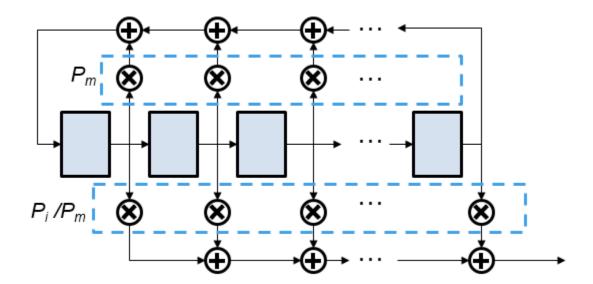

The LTE Convolutional Decoder block implements a wrap-around Viterbi algorithm (WAVA). The input message is cyclically extended to provide training samples for the Viterbi decoder. This algorithm works with tail-biting convolutional encoders, where the encoder state is the same at the beginning and end of a message.

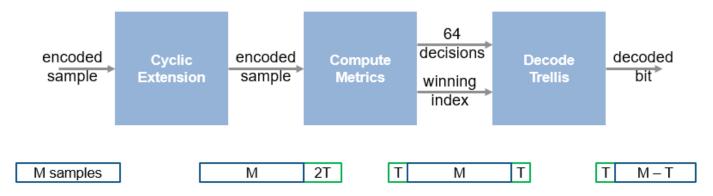

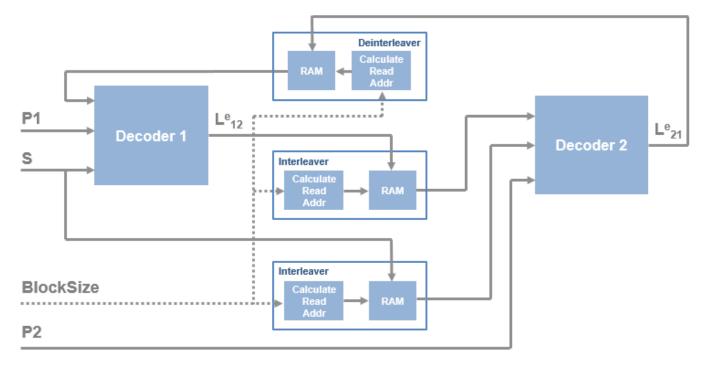

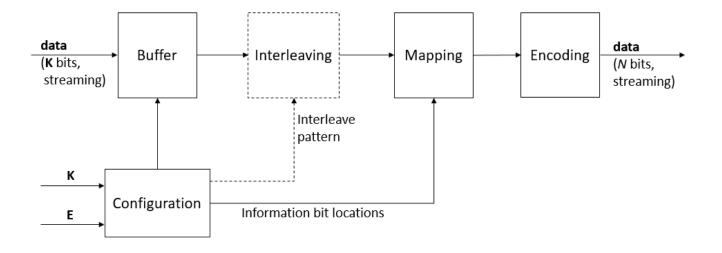

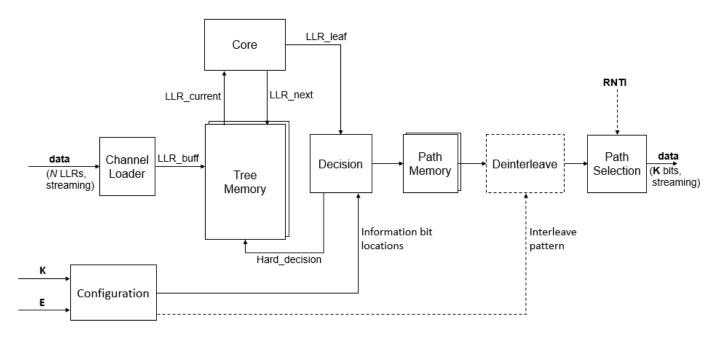

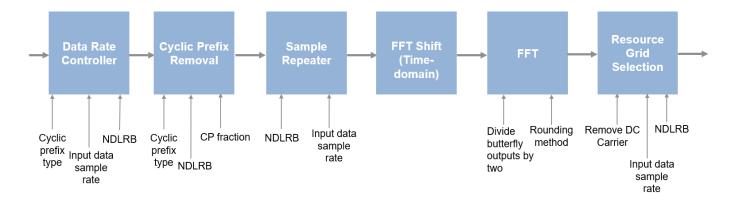

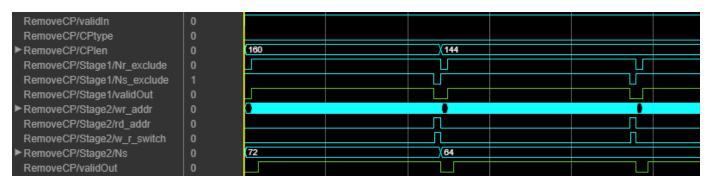

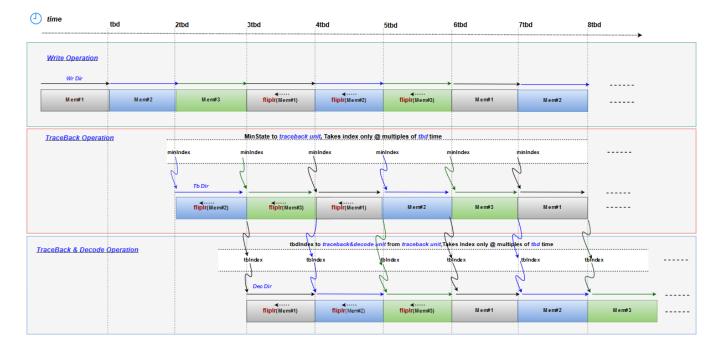

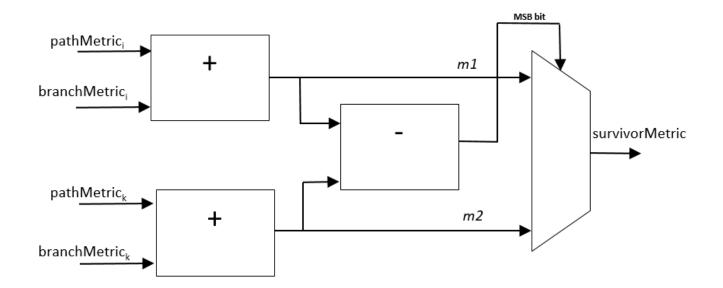

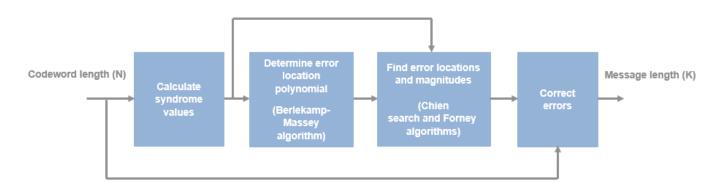

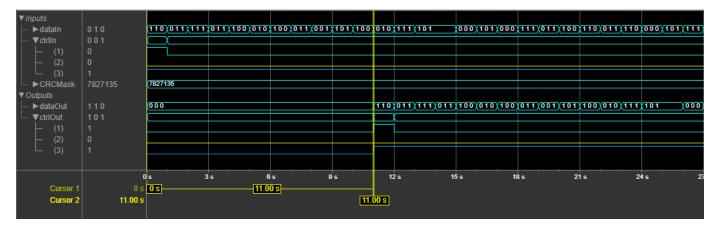

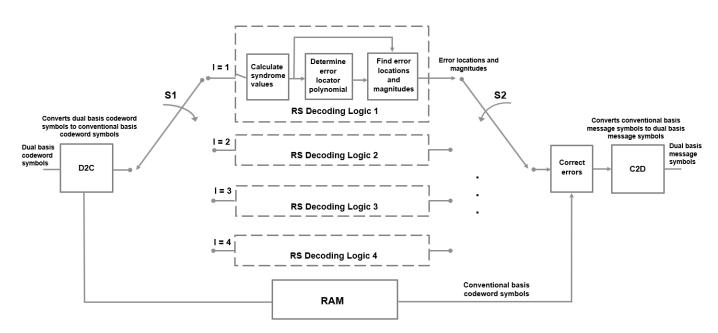

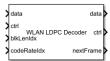

The diagram shows a high-level view of the decoder architecture.

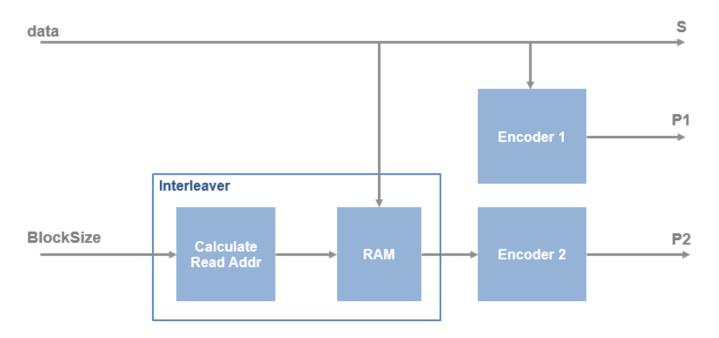

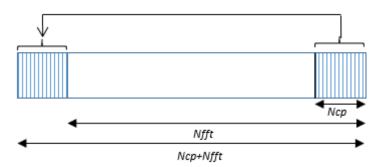

First, the block extends the message by repeating  $2^{*T}$  message samples, where *T* is 40 samples. This value of *T* provides a balance between bit error rate (BER) and optimizing hardware resources. The block uses the extended message to compute branch metrics, state metrics, and branch decisions using add-compare-select operations. The metric word lengths are derived from the data type of the input sample. The block stores a representation of the trellis that is based on the computed decisions. Then it performs traceback decoding. Once the message sample values are decided, the block removes the duplicate training samples and reorders the samples for output.

## Performance

These resource and performance data are the synthesis results from the generated HDL targeted to a Xilinx Zynq-7000 ZC706 board. The implementation is for sfix4 input samples, and a max message size of 1024 (default). HDL code was generated using these options:

- Adaptive pipelining: off

- Minimize clock enables: on

- Reset type: Synchronous

The design achieves a clock frequency of 308.45 MHz.

| Resource              | Uses |

|-----------------------|------|

| LUT                   | 3575 |

| FFS                   | 1776 |

| Xilinx LogiCORE DSP48 | 0    |

| Block RAM (16K)       | 5    |

The input bit width affects the timing and the resources used in metric computation. The maximum message size affects the amount of RAM used in the cyclic extension and traceback stages.

# References

[1] 3GPP TS 36.212. "Multiplexing and channel coding." 3rd Generation Partnership Project; Technical Specification Group Radio Access Network; Evolved Universal Terrestrial Radio Access (E-UTRA). URL: https://www.3gpp.org.

# **Extended Capabilities**

## C/C++ Code Generation

Generate C and C++ code using Simulink  $\mbox{\ensuremath{\mathbb{R}}}$  Coder<sup>TM</sup>.

This block supports C/C++ code generation for Simulink accelerator and rapid accelerator modes and for DPI component generation.

## HDL Code Generation

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder $^{\text{\tiny TM}}$ .

HDL Coder provides additional configuration options that affect HDL implementation and synthesized logic.

This block does not have any HDL Block Properties.

# See Also

**Blocks** LTE Convolutional Encoder

Functions

lteConvolutionalEncode | lteConvolutionalDecode

Introduced in R2017b

# **LTE Convolutional Encoder**

Encode binary samples using tail-biting convolutional algorithm Library: Wireless HDL Toolbox / Error Detection and Correction

# Description

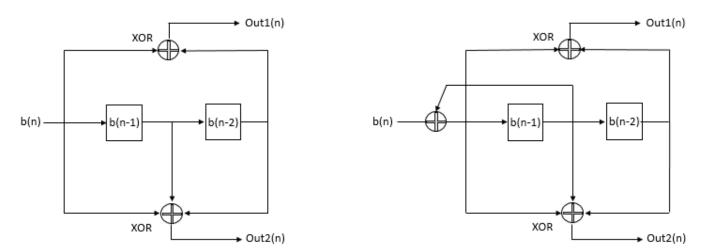

The LTE Convolutional Encoder block implements the encoding polynomials specified by LTE standard TS 36.212 [1]. The convolutional code has constraint length 7 and is tail biting with coding rate 1/3 and octal polynomials G0=133, G1=171 and G2=165. The block provides a hardware-optimized architecture and interface.

This block uses a streaming sample interface with a bus for related control signals. This interface enables the block to operate independently of frame size, and to connect easily with other Wireless HDL Toolbox blocks. The block accepts and returns a value representing a single sample, and a bus containing three control signals. These signals indicate the validity of each sample and the boundaries of the frame. To convert a matrix into a sample stream and these control signals, use the Frame To Samples block or the whdlFramesToSamples function. For a full description of the interface, see "Streaming Sample Interface".

The message size can change dynamically. The encoded output bits for each input bit are returned as a 3-by-1 vector, [G0 G1 G2].

The block takes M + 5 cycles to encode a frame of M samples. Therefore, you must leave M + 5 idle cycles between input frames. Alternatively, you can use the output signal **ctrl.end** to determine when the block is ready for new input.

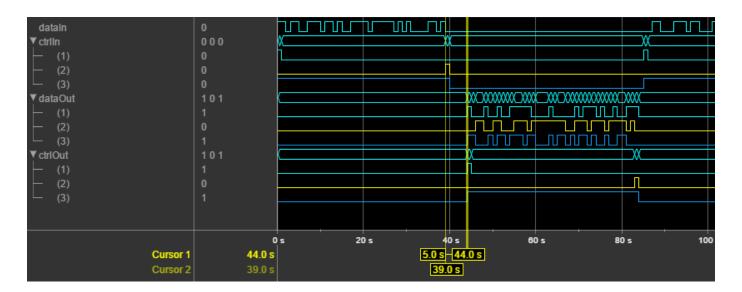

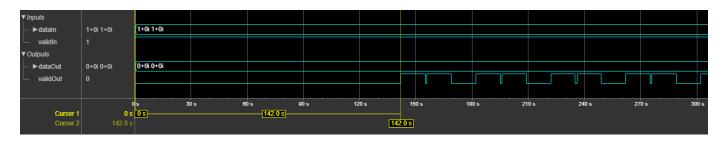

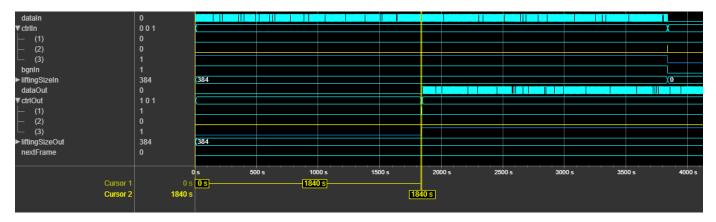

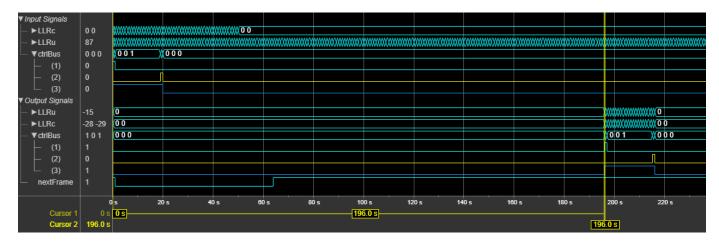

This waveform shows an input message of 40 samples, with 45 idle cycles between frames. The output data is a vector of three encoded bits. The input and output **ctrl** buses are expanded to show the control signals. **start** and **end** show the frame boundaries, and **valid** qualifies the data samples.

# Ports

## Input

## data — Input sample

scalar

Input sample, specified as a binary scalar. double and single are supported for simulation but not for HDL code generation.

Data Types: single | double | Boolean | ufix1

## ctrl — Control signals accompanying sample stream

samplecontrol bus

Control signals accompanying the sample stream, specified as a samplecontrol bus. The bus includes the start, end, and valid control signals, which indicate the boundaries of the frame and the validity of the samples.

- start Indicates the start of the input frame

- end Indicates the end of the input frame

- valid Indicates that the data on the input data port is valid

For more detail, see "Sample Control Bus".

Data Types: bus

## Output

## data — Encoded sample

3-by-1 column vector

Encoded sample, returned as a 3-by-1 column vector. Each encoded sample is represented by three bits, one from each encoder polynomial.

The output data type matches the input data type.

Data Types: single | double | Boolean | ufix1

ctrl — Control signals accompanying sample stream

samplecontrol bus

Control signals accompanying the sample stream, returned as a samplecontrol bus. The bus includes the start, end, and valid control signals, which indicate the boundaries of the frame and the validity of the samples.

- start Indicates the start of the output frame

- end Indicates the end of the output frame

- valid Indicates that the data on the output data port is valid

For more detail, see "Sample Control Bus".

Data Types: bus

## **Parameters**

#### Maximum message length — Maximum input frame size

1024 (default) | positive integer

Maximum input frame size, specified as a positive integer from 6 to  $2^{16}$ . This parameter defines the required amount of frame memory. If you do not specify a power of two, the block uses the next largest power of two.

If an input frame is larger than the specified maximum message length, the block returns a warning.

## Tips

• You cannot use this block inside an Enabled Subsystem or Resettable Subsystem.

## Algorithms

The block implements a tail-biting convolutional encoder as specified by LTE standard TS 36.212 [1].

#### Performance

These resource and performance data are the synthesis results from the generated HDL targeted to a Xilinx Zynq-7000 ZC706 board. The implementation is for a max message size of 1024 (default). The design achieved a clock frequency of 476.2 MHz.

| Resource        | Uses |

|-----------------|------|

| LUT             | 79   |

| LUTRAM          | 16   |

| FFS             | 46   |

| Block RAM (16K) | 0    |

The maximum message size affects the amount of RAM used.

# References

[1] 3GPP TS 36.212. "Multiplexing and channel coding." 3rd Generation Partnership Project; Technical Specification Group Radio Access Network; Evolved Universal Terrestrial Radio Access (E-UTRA). URL: https://www.3gpp.org.

# **Extended Capabilities**

## C/C++ Code Generation

Generate C and C++ code using Simulink® Coder<sup>™</sup>.

This block supports C/C++ code generation for Simulink accelerator and rapid accelerator modes and for DPI component generation.

#### **HDL Code Generation**

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

HDL Coder provides additional configuration options that affect HDL implementation and synthesized logic.

#### **HDL Architecture**

This block has a single, default HDL architecture.

#### **HDL Block Properties**

| ConstrainedOutputPi<br>peline | Number of registers to place at the outputs by moving existing delays<br>within your design. Distributed pipelining does not redistribute these<br>registers. The default is 0. For more details, see<br>"ConstrainedOutputPipeline" (HDL Coder). |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| InputPipeline                 | Number of input pipeline stages to insert in the generated code.<br>Distributed pipelining and constrained output pipelining can move these<br>registers. The default is 0. For more details, see "InputPipeline" (HDL<br>Coder).                 |

| OutputPipeline                | Number of output pipeline stages to insert in the generated code.<br>Distributed pipelining and constrained output pipelining can move these<br>registers. The default is 0. For more details, see "OutputPipeline" (HDL<br>Coder).               |

# See Also

**Blocks** LTE Convolutional Decoder

Functions

teconvolutionalEncode | lteConvolutionalDecode

Introduced in R2017b

# LTE CRC Decoder

Detect errors in input samples using checksumLibrary:Wireless HDL Toolbox / Error Detection and Correction

# Description

The LTE CRC Decoder block calculates a cyclic redundancy check (CRC) and compares it with the appended checksum, for each frame of streaming data samples. You can select from the polynomials specified by LTE standard TS 36.212 [1]. The block provides a hardware-optimized architecture and interface.

This block uses a streaming sample interface with a bus for related control signals. This interface enables the block to operate independently of frame size, and to connect easily with other Wireless HDL Toolbox blocks. The block accepts and returns a value representing a single sample, and a bus containing three control signals. These signals indicate the validity of each sample and the boundaries of the frame. To convert a matrix into a sample stream and these control signals, use the Frame To Samples block or the whdlFramesToSamples function. For a full description of the interface, see "Streaming Sample Interface".

# Ports

Input

## data — Input sample

binary scalar | unsigned integer scalar | binary vector

Input sample, specified as a binary scalar, unsigned integer scalar, or binary vector. The vector size must be less than or equal to the length of the polynomial. The CRC length also must be divisible by the vector size. For example, for polynomial type CRC24A, the valid vector sizes are 24, 12, 8, 6, 4, 3, 2, and 1. An integer input is interpreted as a binary word. For example, vector input  $[0 \ 0 \ 1 \ 0 \ 0 \ 1 \ 0 \ 1 \ 1]$  is equivalent to uint8 input 19.

double and single are supported for simulation but not for HDL code generation.

Data Types: single | double | Boolean | ufix1 | uint8 | uint16 | uint32

## ctrl — Control signals accompanying sample stream

samplecontrol bus

Control signals accompanying the sample stream, specified as a samplecontrol bus. The bus includes the start, end, and valid control signals, which indicate the boundaries of the frame and the validity of the samples.

- start Indicates the start of the input frame

- end Indicates the end of the input frame

• valid — Indicates that the data on the input data port is valid

For more detail, see "Sample Control Bus".

Data Types: bus

#### Output

#### data — Output sample

binary scalar | integer scalar | binary vector

Output sample, returned a binary scalar, unsigned integer scalar, or binary vector of the same data type and size as the input samples. The checksum is removed from the end of the frame.

double and single binary values are supported for simulation but not for HDL code generation.

Data Types: single | double | Boolean | ufix1 | uint8 | uint16 | uint32 | ufixN

#### ctrl — Control signals accompanying sample stream

samplecontrol bus

Control signals accompanying the sample stream, returned as a samplecontrol bus. The bus includes the start, end, and valid control signals, which indicate the boundaries of the frame and the validity of the samples.

- start Indicates the start of the output frame

- end Indicates the end of the output frame

- valid Indicates that the data on the output data port is valid

For more detail, see "Sample Control Bus".

Data Types: bus

#### err — Indicator of checksum mismatch

binary scalar | integer scalar

Indicator of checksum mismatch, returned as a binary scalar or an integer scalar. If you select **Full checksum mismatch**, this port returns the integer XOR result of the calculated checksum against the appended checksum. The **err** value is valid when **ctrl.end** is 1 (true). The data type of this port matches the data type of the input samples.

Data Types: single | double | Boolean | ufix1 | uint8 | uint16 | uint32 | ufixN

# **Parameters**

#### **CRC** Type — Encode polynomial

CRC16 (default) | CRC8 | CRC24A | CRC24B

The encode polynomial options are the four CRC types described in the LTE standard TS 36.212 [1], Section 5.1.1.

Full checksum mismatch — Return bit-by-bit mismatch information

off (default) | on

When this parameter is not selected, the **err** port returns a Boolean value indicating whether any checksum bits are mismatched, after applying **CRC Mask**. When this parameter is selected, the **err** port returns an integer that represents the locations of bit mismatches in the checksum.

### CRC Mask — Mask applied to checksum

0 (default) | integer from 0 to  $2^{CRCLength} - 1$

Mask applied to checksum, specified as an integer representing a binary word from 0 to  $2^{CRCLength}$  – 1. This mask is typically a Radio Network Temporary Identifier (RNTI).

#### Dependencies

This parameter appears when Full checksum mismatch is cleared.

# Algorithms

When you use vector or integer input, the block implements a parallel CRC algorithm [2]. The implementation is the same as the algorithm used by the Communications Toolbox<sup>™</sup> blocks General CRC Generator HDL Optimized and General CRC Syndrome Detector HDL Optimized.

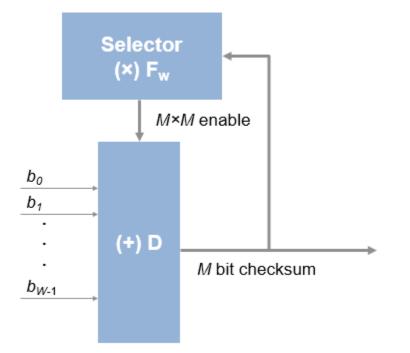

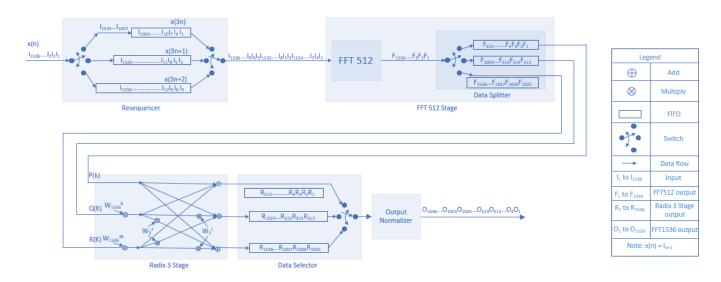

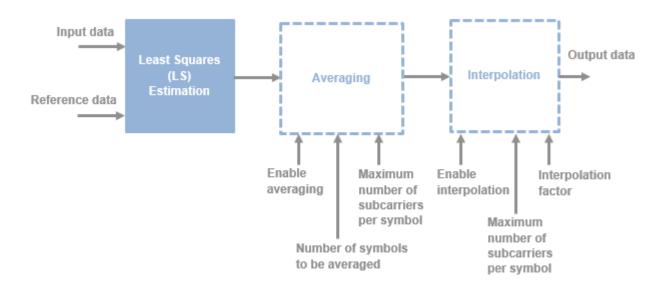

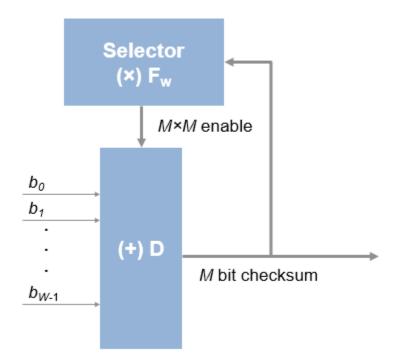

To provide high throughput for modern communications systems, the block implements the CRC algorithm with a parallel architecture. This architecture recursively calculates M bits of a CRC checksum for each W input bits. At the end of the frame, the final checksum result is appended to the message. For a polynomial length of M, the recursive checksum calculation for W bits in parallel is

$X' = F_W(\times)X(+)D.$

$F_W$  is an *M*-by-*M* matrix that selects elements of the current state for the polynomial calculation with the new input bits. *D* is an *M*-element vector that provides the new input bits, ordered in relation to the generator polynomial and padded with zeros. The block implements the (×) with logical AND and (+) with logical XOR.

### Latency

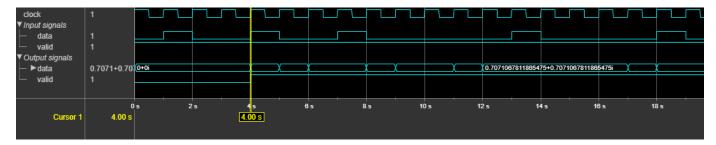

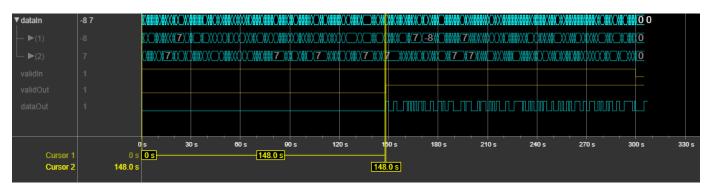

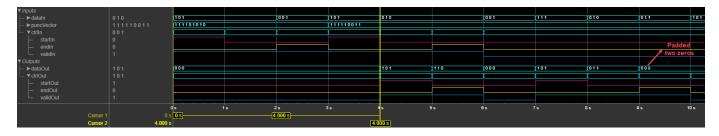

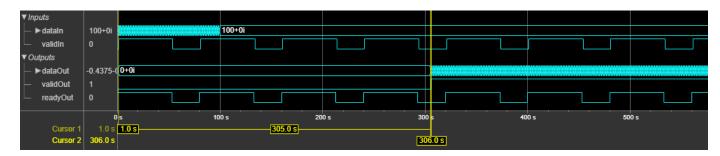

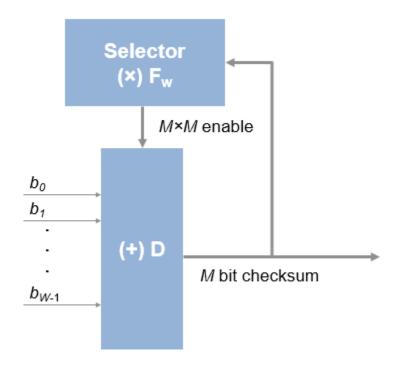

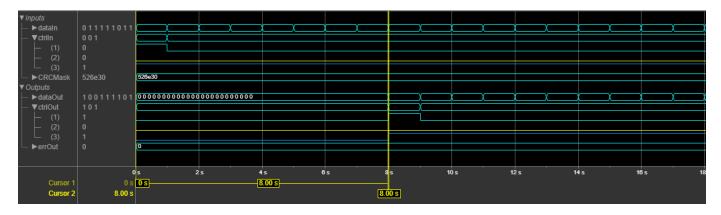

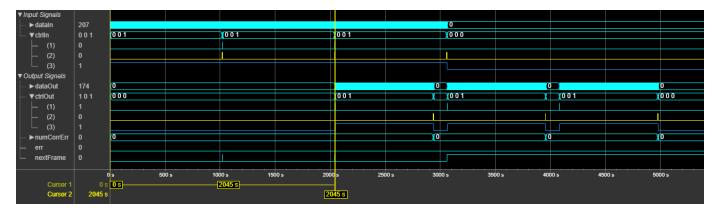

This waveform shows a 40-sample frame, input two samples at a time, encoded with a CRC16 polynomial. There is no gap between input frames. The output stream has removed the checksum, so there are eight cycles between output frames. The latency of the decoder is 3\*CRCLength/InputSize + 5, assuming contiguous valid input samples.

#### Performance